计组复习简答题总结

简答题

- CPU中有哪几类主要寄存器,并用一句话回答其功能。

==答:==数据寄存器(DR);指令寄存器(IR);程序计数器(PC);数据地址寄存器(AR);通用寄存器(R_0~R_3);状态字寄存器(PSW)。

==功能:==执行指令、操作、时间控制以及数据加工。

- 指令和数据都用二进制代码存放在内存中,从时空角度回答CPU如何区分读出的代码是指令还是数据?

==答:==时间上,取值周期从内存中取出的是指令,执行周期从内存取出或写入的是数据;空间上,从内存中取出送往控制器的是指令,从内存中取出送往运算器的是数据。

- ==简述64位安腾处理机的体系结构主要特点==(考的几率极其大)

==答:==显示并行计算技术;超长指令字技术;分支推断技术;推测技术;软件流水技术;寄存器堆栈技术。

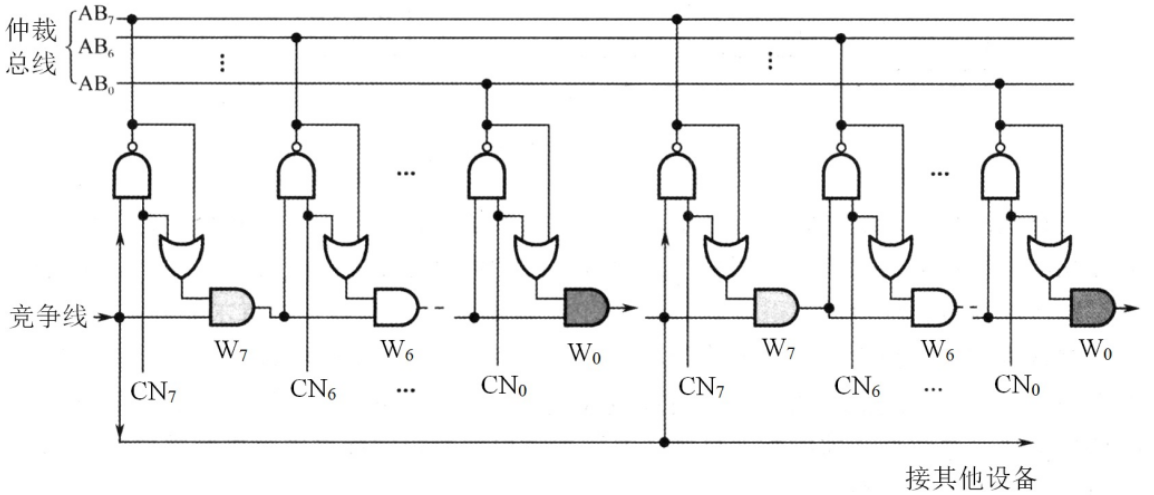

分布式仲裁器的逻辑示意图。

列表比较CISC处理机和RISC处理机

| 比较内容 | CISC | RISC |

|---|---|---|

| 指令系统 | 复杂、庞大 | 简单、精简 |

| 指令数目 | 一般大于200 | 一般小于100 |

| 指令格式 | 一般大于4 | 一般小于4 |

| 寻址方式 | 一般大于4 | 一般小于4 |

| 指令字长 | 不固定 | 等长 |

| 可访存指令 | 不加限定 | 只有LOAD/STORE指令 |

| 各种指令使用频率 | 相差不大 | 相差不大 |

| 各种指令执行时间 | 相差很大 | 绝大多数在一个周期内完成 |

| 优化编译实现 | 很难 | 较容易 |

| 程序源代码长度 | 较短 | 较长 |

| 控制器实现方式 | 绝大多数微程序控制 | 绝大部分是硬布线控制 |

| 软件系统开发时间 | 较短 | 较长 |

- PCI总线三种桥的名称?简述其功能

==答:==HOST/PCI桥(简称HOST桥);PCI/PCI桥;PCI/LAGACY桥

==桥的功能:==连接两条线,使总线间相互通信;桥是一个总线转换部件,可以把一条总线的地址空间映射到另一条总线的地址空间上,从而使系统中任意一个总线主设备都能看到同样的一份地址表;利用桥可以实现总线间的猝发式传送;桥有信号的缓冲组等,能力和信号电平转换功能;它还可以完成规程转换、数据块存化、装拆数据分。

- 计算机系统的层次结构

| 等级 | 层次 | 组成 |

|---|---|---|

| 5级 | 高级语言级 | 编译程序 |

| 4级 | 汇编语言级 | 汇编程序 |

| 3级 | 操作系统级 | 操作系统 |

| 2级 | 一般机器级 | 微程序 |

| 1级 | 微程序设计级 | 直接由硬件执行 |

- 简述水平型微指令和垂直型微指令的特点

| 方面 | 水平型微指令 | 垂直型微指令 |

|---|---|---|

| 并行操作 | 强,效力高,灵活性强 | 较差 |

| 执行一条指令时间 | 短 | 长 |

| 解析指令 | 微指令字长而微程序短 | 微指令字短而微程序长 |

| 用户掌握 | 难 | 易 |

- 哪几种技术手段可以加快存储系统的访问速度

- 增加cache,利用空间局部性和时间局部性减少内存访问时间

- cache优化,多级cache减少缺失损失,非阻塞cache,流水化cache访问

- 采用交叉式存储方式提高内存带宽

- 采用虚拟内存机制降低内存缺失损失

- 一台机器的指令系统有哪几类典型指令

==答:==数据传送类指令;算术运算类指令;逻辑运算类指令;程序控制类指令;

输入输出类指令;字符串类指令;系统控制类指令;特权指令

- 存储系统中加入cache存储器的目的?有哪些地址映射方式,各有什么特点?

==答:==Cache是一种高速缓冲存储器,为了解决CPU与主存之间速度不匹配。

==方式:==全相联映射方式,一种带全部块地址一起保存的方法,可使主存的一块直接拷贝到cache中的任意一行上,非常灵活;直接映射方式: 优点是硬件简单,成本低,缺点是每个主存块只有一个固定的行位置可存放;组相联映射方式:它是前两者的折衷方案,适度的兼顾了二者的优点有尽量避免其缺点,从灵活性、命中率、硬件投资来说较为理想,因而得到了普遍采用。

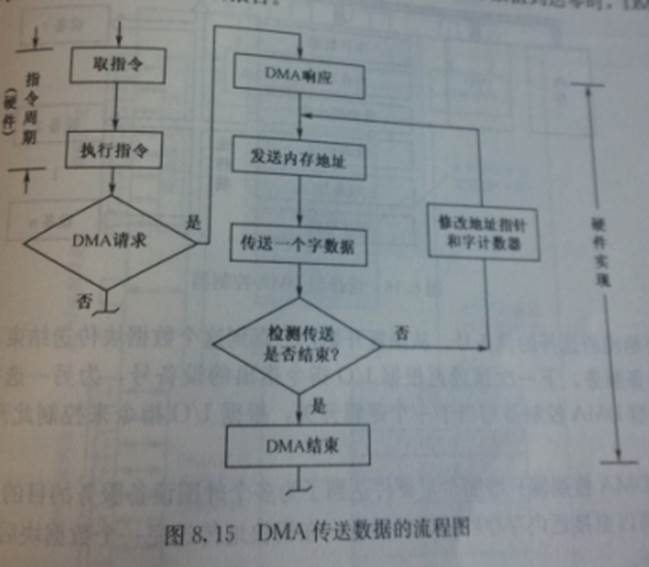

- DMA传送数据流程图

- 安腾处理机的“分支推断”技术的基本思想

==答:==该技术将传统的”if-else-then”分支结构转变为无分支的顺序/并行代码,以避免由于错误预测分支而付出代价。当处理机能够确认分支的所有的可能的后续路径开始并执行多段代码并暂存各段代码的执行结果,直到处理机确认分支转移与否的条件是真是假时,处理机再把应该选择的路径的指令执行结果保留下来。

- 为什么在计算机系统引入DMA方式来交换数据?若使用总线周期挪用方式,DMA控制器占用总线进行数据交换期间,CPU处于何种状态?

==答:==为了减轻CPU对I/O操作的控制,使得CPU的效率有了提高;

==两种情况:==CPU不需要访问内存;I/O访内优先,因为I/O访内有时间要求,前一个I/O数据必须在下一个访内请求到来之前存取完毕。

- 简述磁表面存储器的读/写原理。

==答:==在磁表面存储器中,利用一种称为“磁头”的装置来形成和判别磁层中的不同磁化状态。写入时,利用磁头使载磁体(盘片)具有不同的磁化状态,而在读出时又利用磁头来判别这些不同的磁化状态。

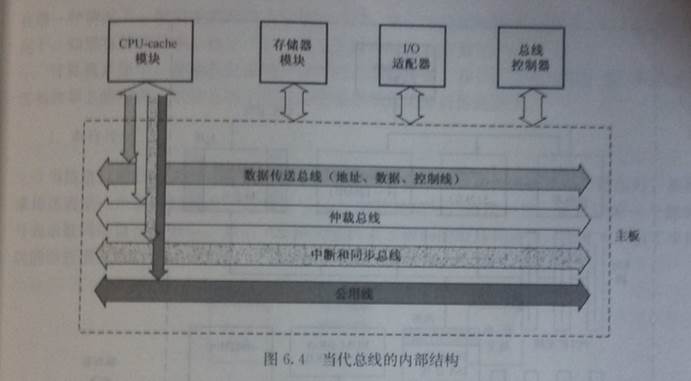

- 画图说明当代总线的内部结构与外部功能部件的联系,做简要说明。

在当代总线结构中,CPU和他私有的cache一起作为一个模块与总线相连。系统中允许有多个这样的处理模块,而总线控制器完成几个总线请求者之间的协调与仲裁

- 比较Cache与虚存的异同

==同:==cache和虚拟存储器都提高了系统性能,应用局部性原理,充分发挥相对高速设备的性能。

==异:==cache是为了解决系统速度问题,虚拟存储器是为了解决主存储器容量问题。cache由硬件实现,对程序员透明,虚拟存储器软硬件共同实现,对系统程序员不透明,对普通程序员透明。